## INTEGRATED CIRCUITS

Preliminary specification

1999 Feb 23

IC25 Data Handbook

XA-SCC

#### **GENERAL DESCRIPTION**

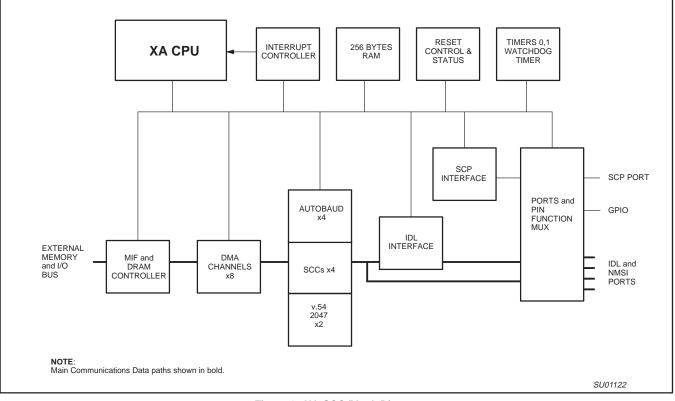

The XA-SCC device is a member of Philips' XA (eXtended Architecture) family of high performance 16-bit single-chip microcontrollers.

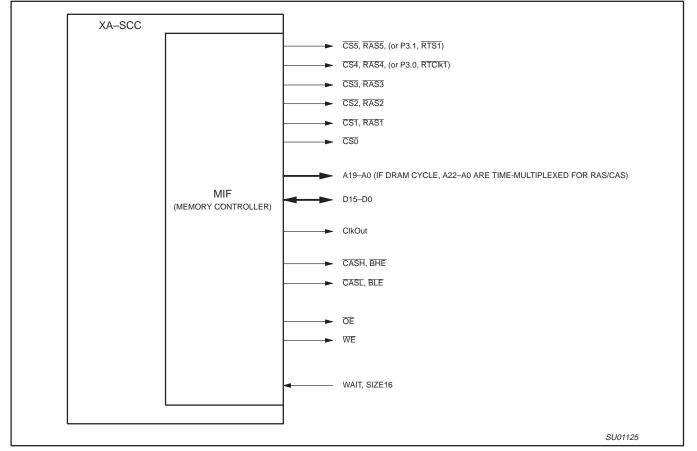

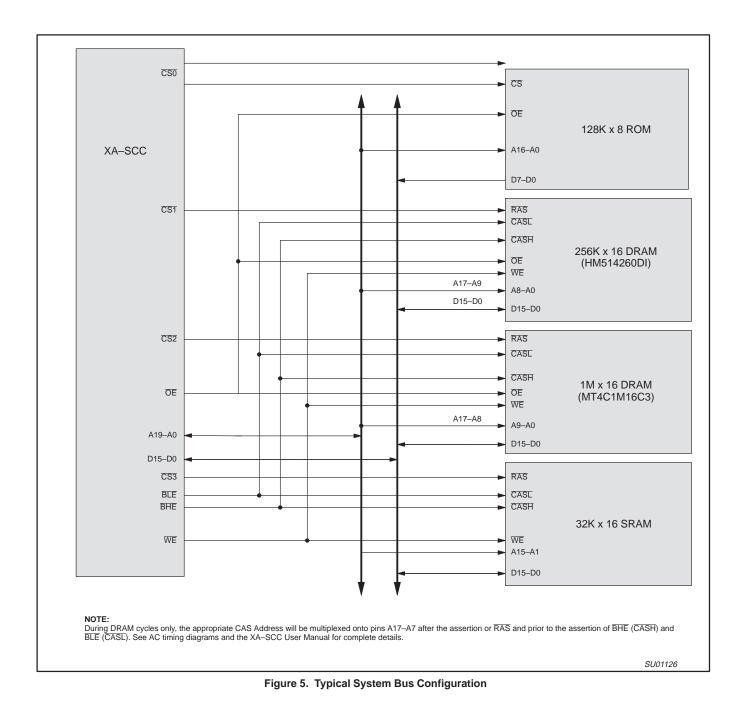

The XA-SCC includes a complete onboard DRAM controller capable of supporting up to 32MegaBytes of DRAM.

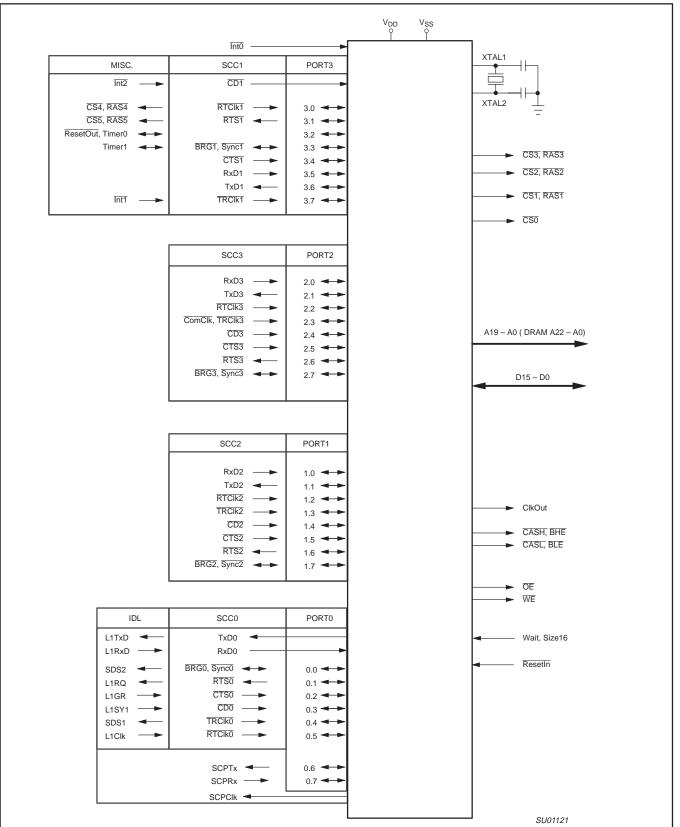

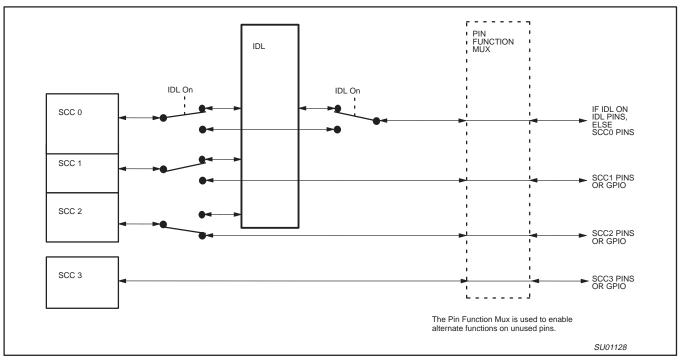

The XA-SCC device combines many powerful communications oriented peripherals on one chip. 4 Full Function SCC's, 8 DMA channels (2 per SCC), hardware autobaud up to 921.6Kbps, IDL TDM interface, two timers/counters, 1 watchdog timer, and multiple general purpose I/O ports. It is suited for many high performance embedded communications functions, including ISDN terminal adaptors and Asynchronous Muxes.

#### SPECIFIC FEATURES OF THE XA-SCC

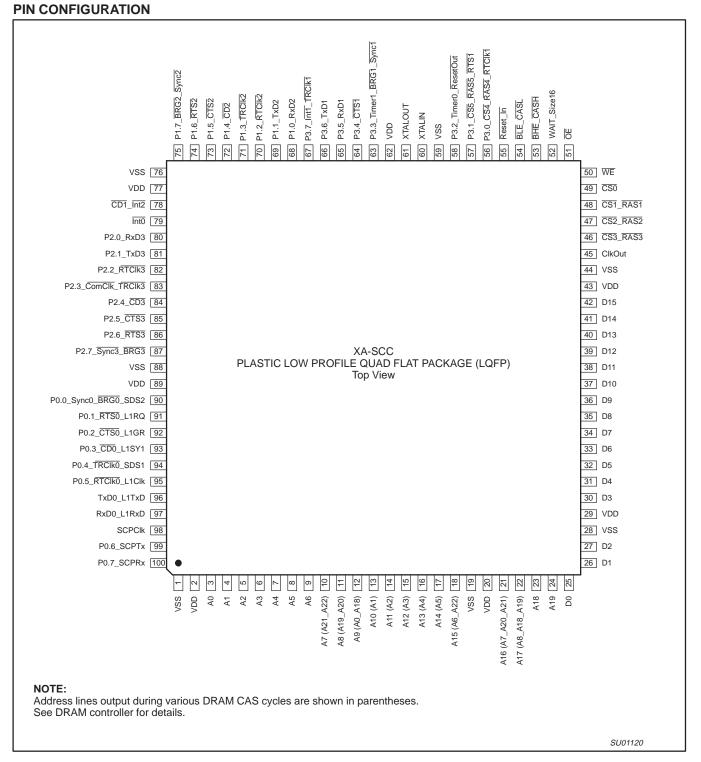

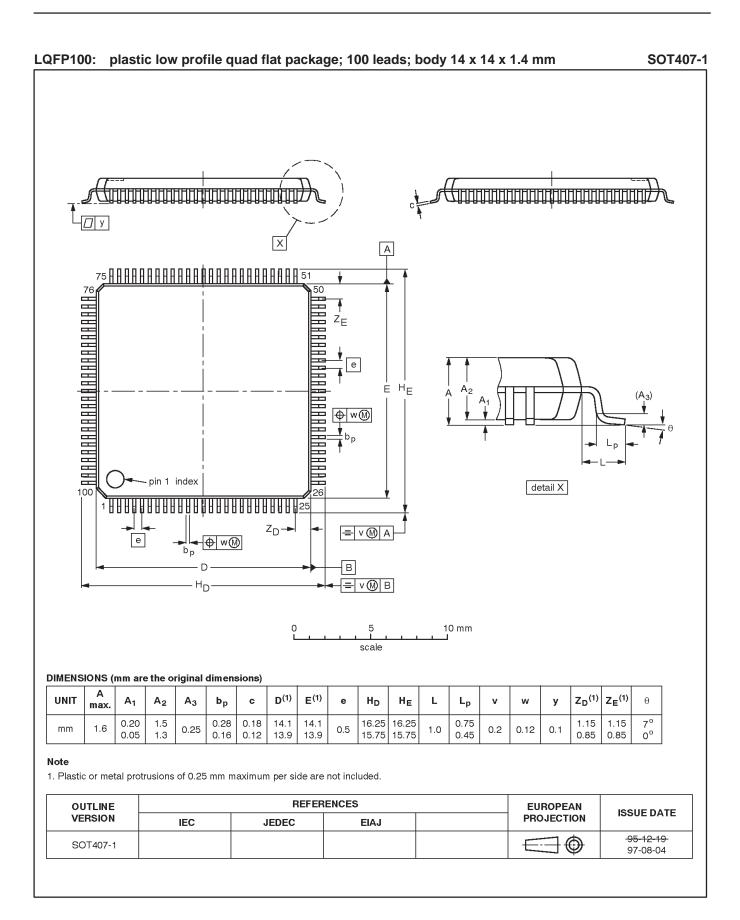

- 3.3V to 5.5V operation to 30MHz over the industrial temperature range, available in 100 pin LQFP package.

- 4 onboard SCC's for 2B+D plus Asynch port, or any combination of 4 sync/async ports. Industry standard IDL and SCP interfaces for glueless connection to U-Chip or S/T chip. Sync data rates to 4Mbps. Asynch data rates to 921.6Kbps with/without autobaud.

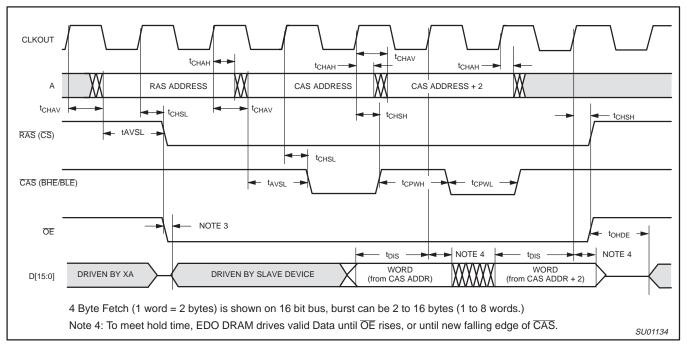

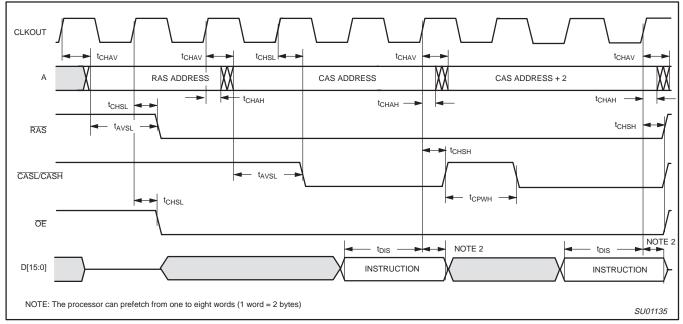

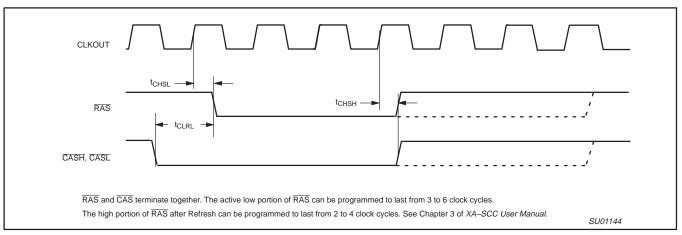

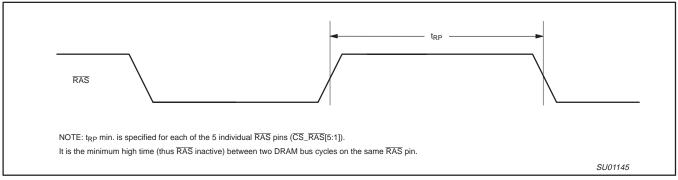

- Complete onboard DRAM controller supports 5 banks of up to 8MBytes each. Interfaces without glue chips to most industry standard DRAMs.

- Memory controller also generates 6 chip selects to support SRAM, ROM, Flash, EPROM, peripheral chips, etc. without external glue.

- Supports off-chip addressing up to 32 MB (2 x 2\*\*24 address spaces) in Harvard architecture, or 16MB in unified memory configuration.

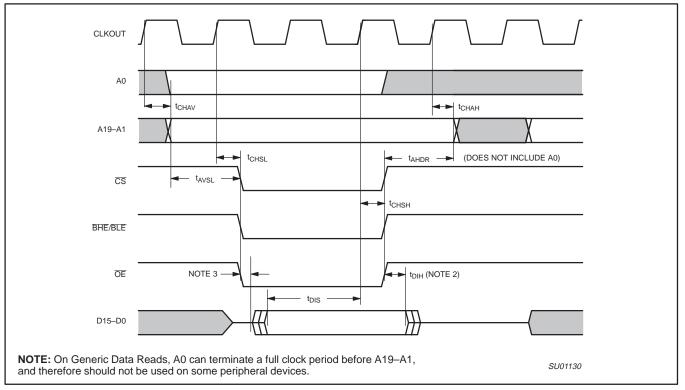

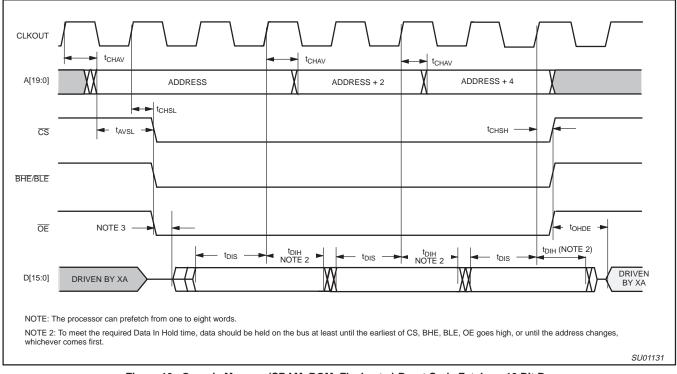

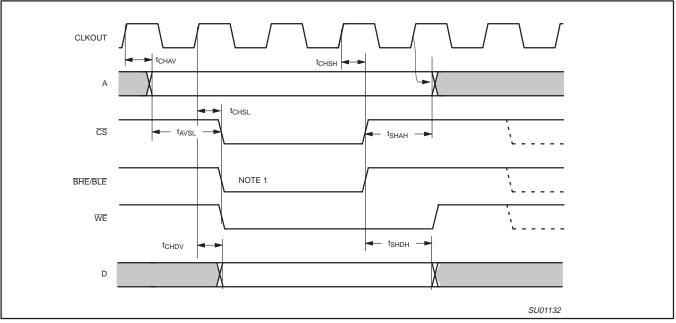

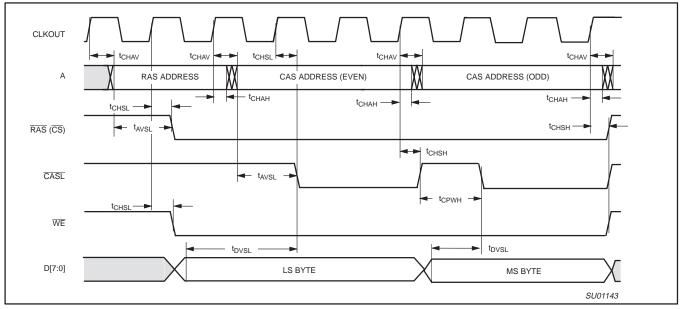

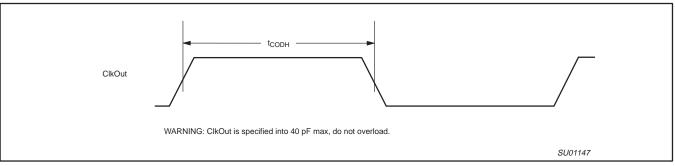

- A clock output reference "ClkOut" is added to simplify external bus interfacing.

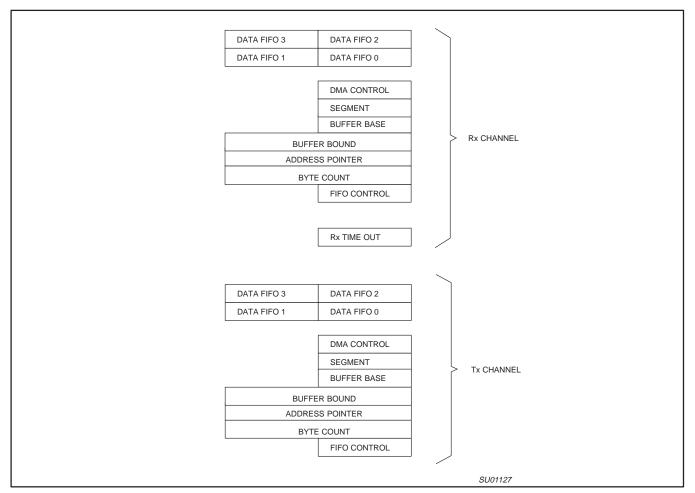

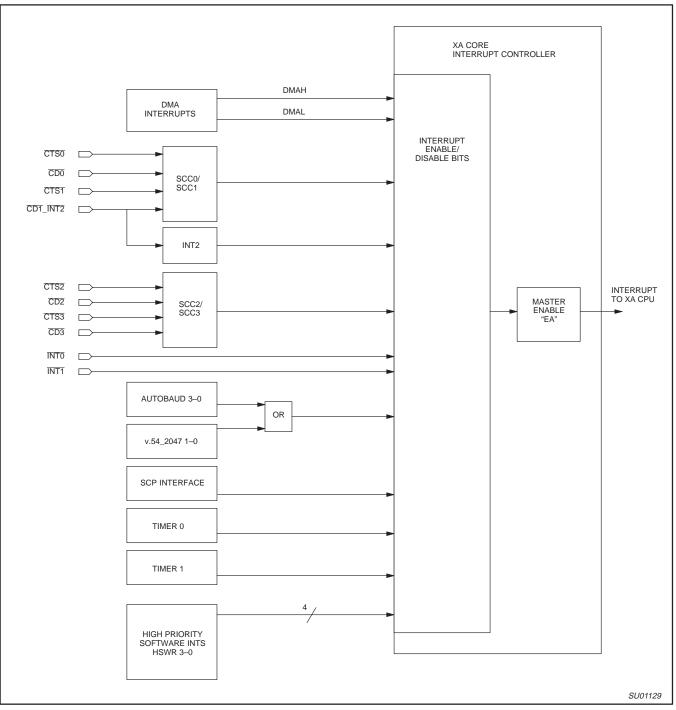

- High performance 8-channel DMA Controller offloads the CPU for moving data to/from SCC's and memory.

- Two standard counter/timers with enhanced features (same as XA-G3 T0, T1). Both timers have a toggle output capability.

- Watchdog timer.

- Seven standard software interrupts, plus four High Priority Software Interrupts, plus 7 levels of Hardware Event Interrupts.

- Active low reset output pin indicates all internal reset occurrences (watchdog reset and the RESET instruction). A reset source register allows program determination of the cause of the most recent reset.

- 32 General Purpose I/O pins, each with 4 programmable output configurations.

- Power saving operating modes: Idle and Power-Down. Wake-Up from power-down via an external interrupt is supported.

#### **ORDERING INFORMATION**

| ROMIess Only | TEMPERATURE RANGE °C AND PACKAGE                      | FREQ (MHz) | PACKAGE DRAWING NUMBER |

|--------------|-------------------------------------------------------|------------|------------------------|

| PXASCCKFBE   | -40 to +85, 100-pin Low Profile Quad Flat Pkg. (LQFP) | 30         | SOT407-1               |

NOTE:

1. K=30MHz, F = (-40 to +85 °C), BE = LQFP

Philips Semiconductors

#### LOGIC SYMBOL

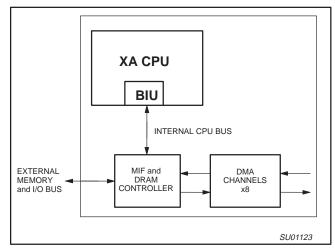

#### **BLOCK DIAGRAM**

Figure 1. XA-SCC Block Diagram

XA-SCC

### CMOS 16-bit communications microcontroller

#### **PIN DESCRIPTIONS**

| MNEMONIC             | LQFP<br>PIN NO.                    | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|----------------------|------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| V <sub>SS</sub>      | 1, 19,<br>28, 44,<br>59, 76,<br>88 | I    | Ground: 0V reference.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| V <sub>DD</sub>      | 2, 20,<br>29, 43,<br>62, 77,<br>89 | I    | <b>Power Supply</b> : This is the power supply voltage for normal, idle, and power down operation.                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| ResetIn              | 55                                 | I    | <b>Reset</b> : A low on this pin resets the microcontroller, causing I/O ports and peripherals to take on their default states, and the processor to begin execution at the address contained in the reset vector.                                                                                                                                                                                                     |  |  |  |  |  |  |  |

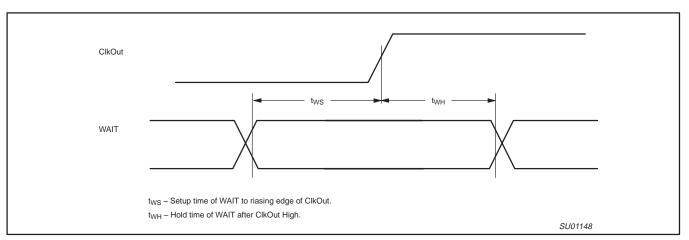

| WAIT/Size16          | 52                                 | I    | <b>Wait/Size16</b> : During Reset, this input determines bus size for boot device $(1 = 16 \text{ bit boot device}, 0 = 8 \text{ bit.})$ During normal operation this is the Wait input $(1 = \text{Wait}, 0 = \text{Proceed.})$                                                                                                                                                                                       |  |  |  |  |  |  |  |

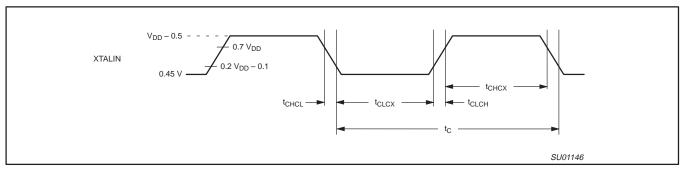

| XTALIn               | 60                                 | I    | <b>Crystal 1</b> : Input to the inverting amplifier used in the oscillator circuit and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| XTALOut              | 61                                 | 1    | Crystal 2: Output from the oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| CSO                  | 49                                 | 0    | <b>Chip Select 0</b> : This output provides the active low chip select to the boot device (usually ROM or Flash.) It cannot be connected to DRAM. From reset, it is enabled and mapped to an address range based at 000000h. It can be remapped to a higher base in the address map (see the Memory Interface chapter in the XA-SCC User Manual.)                                                                      |  |  |  |  |  |  |  |

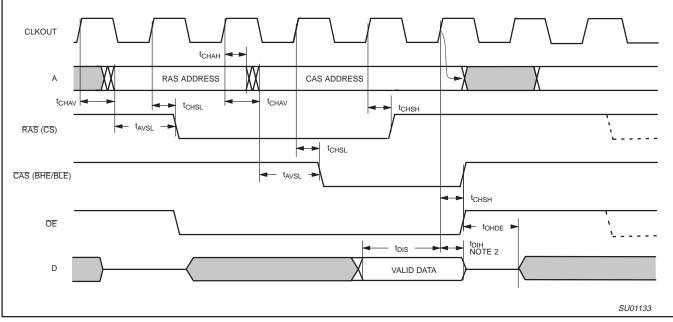

| CS1_RAS1             | 48                                 | 0    | Chip Select 1, RAS 1: Chip selects 1 through 5 come out of reset disabled. They can be programmed to function as normal chip selects, or as RAS strobes to DRAM. CS1 can be "swapped" with CS0 (see the SWAP operation and control bit in the Memory Controller chapter of the XA-SCC User Manual.) CS1 is usually mapped to be based at 000000h eventually, but is capable of being based anywhere in the 16MB space. |  |  |  |  |  |  |  |

| CS2_RAS2             | 47                                 | 0    | <b>CS2</b> , <b>RAS 2</b> : Active low chip selects CS1 through CS5 come out of reset disabled. They can be programmed to function as normal chip selects, or as RAS strobes to DRAM. CS2 through CS5 are not used with the "SWAP" operation (see Memory Controller chapter in the XA-SCC User Manual.) They are mappable to any region of the 16MB address space.                                                     |  |  |  |  |  |  |  |

| CS3_RAS3             | 46                                 | 0    | CS3, RAS 3: See chip select 2 for description.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| see pins 56,57<br>se | for 2 more<br>lects                | chip |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| WE                   | 50                                 | 0    | Write Enable: Goes active low during all bus write cycles only.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| ŌĒ                   | 51                                 | 0    | Output Enable: Goes active low during all bus read cycles only.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| BLE_CASL             | 54                                 | 0    | Byte Low Enable or CAS_Low_Byte: Goes active low during all bus cycles that access D7–D0, read or write, Generic or DRAM. Functions as CAS during DRAM cycles.                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| BHE_CASH             | 53                                 | 0    | Byte High Enable or CAS_High_Byte: Goes active low during all bus cycles that access D15–D8, read or write, Generic or DRAM. Functions as CAS during DRAM cycles.                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| ClkOut               | 45                                 | 0    | <b>Clock Output</b> : This pin outputs a buffered version of the internal CPU clock. The clock output may be used in conjunction with the external bus to synchronize WAIT state generators, etc. The clock output may be disabled by software. <b>WARNING</b> : The capacitive loading on this output must not exceed 40pF.                                                                                           |  |  |  |  |  |  |  |

| A19–A0               | 24–21,<br>18–3                     | 0    | Address[19:0]: These address lines output a19–a0 during generic (SRAM etc) bus cycles. DRAMs are connected only to pins 22,21, 18–10 (pins A17 to A7; see User Manual MIF Chapter for connecting various DRAM sizes); the appropriate address values are multiplexed onto these 11 pins for RAS and CAS during DRAM bus cycles.                                                                                        |  |  |  |  |  |  |  |

| D15–D0               | 42–30,<br>27–25                    | I/O  | Data[15:0]: Bi-directional data bus, D15–D0.                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| P0.0 <sup>1</sup>    | 90                                 | I/O  | P0.0_Sync0_BRG0_SDS2: Port 0 Bit 0, or SCC0 Sync input or output, or SCC0 BRG output, or SCC0 TxClk output, or IDL SDS2 output.                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| P0.1 <sup>1</sup>    | 91                                 | I/O  | <b>P0.1_RTS0_L1RQ</b> : Port0 Bit1 , or SCC0 RTS (Request to send) output, or IDL L1RQ (D Channel Request) output.                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| P0.2 <sup>1</sup>    | 92                                 | I/O  | P0.2_CTS0_L1GR: Port 0 Bit2, or SCC0 CTS (Clear to Send) input or IDL L1GR (D Channel Grant) input                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| P0.3 <sup>1</sup>    | 93                                 | I/O  | P0.3_CD0_L1SY1: Port 0 Bit 3, or SCC0 Carrier Detect input, or IDL Sync input.                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| P0.4 <sup>1, 2</sup> | 94                                 | I/O  | P0.4_TRCIk0_SDS1: Port 0 Bit 4, or SCC0 TR clock input, or IDL SDS1 output.                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

XA-SCC

| MNEMONIC             | LQFP<br>PIN NO. | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0.5 <sup>1, 2</sup> | 95              | I/O  | P0.5_RTCIk0_L1CIk: Port 0 Bit 5, or SCC0 RT clock input, or IDL Clock input.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| P0.6 <sup>1</sup>    | 99              | I/O  | P0.6_SCPTx: Port 0 Bit 6, or SCP interface Transmit data output.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P0.7 <sup>1</sup>    | 100             | I/O  | P0.7_SCPRx: Port 0 Bit 7, or SCP interface Receive data input.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TxD0_L1TxD           | 96              | 0    | TxD0_L1Txd: Transmit data for SCC0 in NMSI mode, or for IDL bus                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RxD0_L1RxD           | 97              | 1    | RxD0_L1Rxd: Receive data for SCC0 in NMSI mode, or for IDL bus                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SCPClk               | 98              | 0    | SCPCIk: This output provides the gated clock for the SCP bus.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| P1.0                 | 68              | I/O  | P1.0_RxD2: Port 1 Bit 0, or SCC2 RxD input                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| P1.1                 | 69              | I/O  | P1.1_TxD2: Port 1 Bit 1, or SCC2 TxD output                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P1.2 <sup>2</sup>    | 70              | I/O  | P1.2_RTCIk2: Port 1 Bit 2, or SCC2 RT Clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P1.3 <sup>2</sup>    | 71              | I/O  | P1.3_TRCIk2: Port 1 Bit 3, or SCC2 TR Clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P1.4                 | 72              | I/O  | P1.4_CD2: Port 1 Bit 4, or SCC2 Carrier Detect input                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P1.5                 | 73              | I/O  | P1.5_CTS2: Port 1 Bit 5, or SCC2 Clear To Send input                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P1.6                 | 74              | I/O  | P1.6_RTS2: Port 1 Bit 6, or SCC2 Request To Send output                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| P1.7                 | 75              | I/O  | P1.7_BRG2_Sync2: Port 1 Bit 7, or SCC2 Sync input or output, or BRG output, or TxClk output (see SCC clocks diagrams in User Manual Chp 5)                                                                                                                                                                                                                                                                                                                                                              |

| P2.0                 | 80              | I/O  | P2.0_RxD3: Port 2 Bit 0, or SCC3 Rx Data input                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P2.1                 | 81              | I/O  | P2.1_TxD3: Port 2 Bit 1, or SCC3 Tx Data output                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P2.2 <sup>2</sup>    | 82              | I/O  | P2.2_RTCIk3: Port 2 Bit 2, or SCC3 RT Clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P2.3 <sup>2</sup>    | 83              | I/O  | P2.3_ComClk_TRClk3: Port 2 Bit 3, or SCC3 TR Clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| P2.4                 | 84              | I/O  | P2.4_CD3: Port 2 Bit 4, or SCC3 Carrier Detect input                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P2.5                 | 85              | I/O  | P2.5_CTS3: Port 2 Bit 5, or SCC3 Clear To Send input                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P2.6                 | 86              | I/O  | P2.6_RTS3: Port 2 Bit 6, or SCC3 Request To Send output                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| P2.7                 | 87              | I/O  | P2.7_Sync3_BRG3: Port 2 Bit 7, or SCC3 Sync input or output, or BRG output, or TxClk output (see SCC clocks diagrams in User Manual Chp 5)                                                                                                                                                                                                                                                                                                                                                              |

| P3.0 <sup>2</sup>    | 56              | I/O  | P3.0_CS4_RAS4_RTCIk1: Port 3 Bit 0, or CS4 or RAS4 output, or SCC1 RT Clock input                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P3.1                 | 57              | I/O  | P3.1_CS5_RAS5_RTS1: Port 3 Bit 1, or CS5 or RAS5 output, or SCC1 Request To Send output                                                                                                                                                                                                                                                                                                                                                                                                                 |

| P3.2                 | 58              | I/O  | P3.2_Timer0_ResetOut: Port 3 Bit 2, or Timer0 input or output, or ResetOut output.                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                      |                 |      | <b>ResetOut</b> : If the ResetOut function is selected, this pin outputs a low whenever the XA-SCC processor is reset by an <b>internal</b> source (watchdog reset or the RESET instruction.) <b>WARNING</b> : Unlike the other 31 GPIO pins, during power up reset, this pin can output a strongly driven low pulse. The duration of this low pulse ranges from 0ns to 258 system clocks, starting at the time that V <sub>CC</sub> is valid. The state of the ResetIn pin does not affect this pulse. |

|                      |                 |      | When used as GPIO, this pin can also be driven low by software without resetting the XA-SCC.                                                                                                                                                                                                                                                                                                                                                                                                            |

| P3.3                 | 63              | I/O  | P3.3_Timer1_BRG1_Sync1: Port 3 Bit 3, or Timer1 input or output, or SCC1 BRG output, or SCC1 Sync input or output                                                                                                                                                                                                                                                                                                                                                                                       |

| P3.4                 | 64              | I/O  | P3.4_CTS1: Port 3 Bit 4, or SCC1 Clear To Send input                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P3.5                 | 65              | I/O  | P3.5_RxD1: Port 3 Bit 5, or SCC1 Receive Data input                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P3.6                 | 66              | I/O  | P3.6_TxD1: Port 3 Bit 6, or SCC1 Transmit Data output                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P3.7 <sup>2</sup>    | 67              | I/O  | P3.7_Int1_TRCIk1: Port 3 Bit 7, or External Interrupt1 input, or SCC1 TR Clock input                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CD1_Int2             | 78              | I    | CD1_Int2: SCC1 Carrier Detect, or External Interrupt 2                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Int0                 | 79              | 1    | External Interrupt 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

NOTES:

1. See XA-SCC User Guide "Pins Chapter" for how to program selection of pin functions.

2. RTClk input is usually used for Rx Clock if an external clock is needed, but can be used for either Rx or Tx or both. TRClk is usually used for Tx Clock, but can be used for Rx or Tx or both.

1999 Feb 23

## CMOS 16-bit communications microcontroller

#### CONTROL REGISTER OVERVIEW

There are two types of control registers in the XA-SCC, these are SFRs (Special Function Registers), and MMRs (Memory Mapped Registers.) The SFR registers, with the exception of MRBL, MRBH, MICFG, BCR, BRTH, BRTL, and RSTSRC are the standard XA core registers. See **WARNINGs about BCR, BRTH, and BRTL in the Table below.**

SFRs are accessed by "direct addressing" only (see IC25 XA User Manual for direct addressing.) The MMRs are specific to the XA-SCC on board peripherals, and can be accessed by any addressing mode that can be used for off chip data accesses. The MMRs are implemented in a relocatable block. See the MIF chapter in the XA-SCC User Manual for details on how to relocate the MMRs by writing a new base address into the MRBL and MRBH (MMR Base Low and High) registers.

#### Table 1. Special Function Registers (SFR)<sup>1, 2, 3</sup>

| NAME   | DESCRIPTION                                   | SFR<br>Address | MSE                | BIT FUNCTIONS AND ADDRESSES MSB LSB |                                |                             |                              |                           |                             |        |     |  |

|--------|-----------------------------------------------|----------------|--------------------|-------------------------------------|--------------------------------|-----------------------------|------------------------------|---------------------------|-----------------------------|--------|-----|--|

| BCR    | Bus Configuration Reg<br>RESERVED—see warning | 46Ah           | WARNIN<br>07h, the | G—Never w<br>only legal v           | rite to the E<br>alue. This is | BCR registers not the sar   | r in the XA-<br>ne as for ot | SCC part—i<br>her XA deri | t is initialize<br>vatives. | ed to  | 07h |  |

| BTRH   | Bus Timing Reg High                           | 469h           |                    | G—Immedia                           | ately after r                  | eset, always<br>v these two | write BTRI                   | H = 51h, foll             | owed by wi                  | riting | FFh |  |

| BTRL   | Bus Timing Reg Low                            | 468h           | same as            | for other XA                        | A derivative                   | s.                          | writes with                  | ive NOF3.                 | 1115 15 1100                | ule    | EFh |  |

|        |                                               |                |                    |                                     |                                |                             |                              |                           |                             |        |     |  |

| MRBL#  | MMR Base Address Low                          | 496h           | MA15               | MA14                                | MA13                           | MA12                        | -                            | -                         | -                           | MRBE   | x0h |  |

| MRBH#  | MMR Base Address High                         | 497h           | MA23               | MA22                                | MA21                           | MA20                        | MA19                         | MA18                      | MA17                        | MA16   | xx  |  |

| MICFG# | ClkOut Tri-St Enable<br>1 = Enabled           | 499h           | -                  | -                                   | -                              | -                           | -                            | -                         | -                           | CLKOE  | 01h |  |

| CS     | Code Segment                                  | 443h           |                    |                                     |                                |                             |                              |                           |                             |        | 00h |  |

| DS     | Data Segment                                  | 441h           |                    |                                     |                                |                             |                              |                           |                             |        | 00h |  |

| ES     | Extra Segment                                 | 442h           |                    |                                     |                                |                             |                              |                           |                             |        | 00h |  |

|        |                                               |                |                    |                                     |                                |                             |                              |                           |                             |        |     |  |

|        |                                               |                | 33F                | 33E                                 | 33D                            | 33C                         | 33B                          | 33A                       | 339                         | 338    |     |  |

| IEH*   | Interrupt Enable High                         | 427h           | EHSWR3             | EHSWR2                              | EHSWR1                         | EHSWR0                      | ESCP                         | EAuto                     | ESC23                       | ESC01  | 00h |  |

|        |                                               |                | 337                | 336                                 | 335                            | 334                         | 333                          | 332                       | 331                         | 330    |     |  |

| IEL*   | Interrupt Enable Low                          | 426h           | EA                 | EDMAH                               | EDMAL                          | EX2                         | ET1                          | EX1                       | ET0                         | EX0    | 00h |  |

| IPA0   | Interrupt Priority A0                         | 4A0h           | -                  |                                     | PT0                            |                             | -                            |                           | PX0                         |        | 00h |  |

| IPA1   | Interrupt Priority A1                         | 4A1h           | -                  |                                     | PT1                            |                             | -                            |                           | PX1                         |        | 00h |  |

| IPA2   | Interrupt Priority A2                         | 4A2h           | -                  |                                     | PDMAL                          |                             | -                            |                           | PX2                         |        | 00h |  |

| IPA3   | Interrupt Priority A3                         | 4A3h           |                    | Rese                                | erved                          |                             | -                            |                           | PDMAH                       |        | 00h |  |

| IPA4   | Interrupt Priority A4                         | 4A4h           | -                  |                                     | PSC23                          |                             | -                            |                           | PSC01                       |        | 00h |  |

| IPA5   | Interrupt Priority A5                         | 4A5h           | -                  |                                     | PSCP                           |                             | -                            |                           | PAutoB                      |        | 00h |  |

| IPA6   | Interrupt Priority A6                         | 4A6h           | -                  |                                     | PHSWR1                         |                             | -                            |                           | PHSWR0                      |        | 00h |  |

| IPA7   | Interrupt Priority A7                         | 4A7h           | -                  |                                     | PHSWR3                         |                             | -                            |                           | PHSWR2                      |        | 00h |  |

|        |                                               |                | 387                | 386                                 | 385                            | 384                         | 383                          | 382                       | 381                         | 380    |     |  |

| P0*    | Port 0                                        | 430h           |                    |                                     |                                |                             | -                            |                           |                             |        | FFh |  |

|        |                                               |                | 38F                | 38E                                 | 38D                            | 38C                         | 38B                          | 38A                       | 389                         | 388    |     |  |

| P1*    | Port 1                                        | 431h           |                    |                                     |                                |                             |                              |                           |                             |        | FFh |  |

|        |                                               |                | 397                | 396                                 | 395                            | 394                         | 393                          | 392                       | 391                         | 390    |     |  |

| P2*    | Port 2                                        | 432h           |                    |                                     |                                |                             |                              |                           |                             |        | FFh |  |

1999 Feb 23

## CMOS 16-bit communications microcontroller

| NAME   | DESCRIPTION              | SFR<br>Address | BIT FUNCTIONS AND ADDRESSES MSB LSB |       |       |       |       |       |           |            |        |  |

|--------|--------------------------|----------------|-------------------------------------|-------|-------|-------|-------|-------|-----------|------------|--------|--|

|        |                          |                | 39F                                 | 39E   | 39D   | 39C   | 39B   | 39A   | 399       | 398        |        |  |

| P3*    | Port 3                   | 433h           |                                     |       |       |       |       |       |           |            | FFh    |  |

| P0CFGA | Port 0 Configuration A   | 470h           |                                     |       |       |       |       |       |           |            | Note 4 |  |

| P1CFGA | Port 1 Configuration A   | 471h           |                                     |       |       |       |       |       |           |            | Note 4 |  |

| P2CFGA | Port 2 Configuration A   | 472h           |                                     |       |       |       |       |       |           |            | Note 4 |  |

| P3CFGA | Port 3 Configuration A   | 473h           |                                     |       |       |       |       |       |           |            | Note 4 |  |

| P0CFGB | Port 0 Configuration B   | 4F0h           |                                     |       |       |       |       |       |           |            | Note 4 |  |

| P1CFGB | Port 1 Configuration B   | 4F1h           |                                     |       |       |       |       |       |           |            | Note 4 |  |

| P2CFGB | Port 2 Configuration B   | 4F2h           |                                     |       |       |       |       |       |           |            | Note 4 |  |

| P3CFGB | Port 3 Configuration B   | 4F3h           |                                     |       |       |       |       |       |           |            | Note 4 |  |

|        |                          |                | 007                                 | 000   | 005   | 004   | 000   | 000   | 001       | 000        | ]      |  |

| PCON*  | Power Control Reg        | 404h           | 227                                 | 226   | 225   | 224   | 223   | 222   | 221<br>PD | 220<br>IDL | 00h    |  |

| FCON   | Fower Control Reg        | 40411          |                                     | -     | -     | -     | -     | -     | FD        | IDL        | 0011   |  |

|        |                          |                | 20F                                 | 20E   | 20D   | 20C   | 20B   | 20A   | 209       | 208        | 1      |  |

| PSWH*  | Program Status Word High | 401h           | SM                                  | TM    | RS1   | RS0   | IM3   | IM2   | IM1       | IM0        | Note 5 |  |

|        |                          |                | 207                                 | 206   | 205   | 204   | 203   | 202   | 201       | 200        | 1      |  |

| PSWL*  | Program Status Word Low  | 400h           | С                                   | AC    | -     | -     | -     | V     | N         | Z          | Note 5 |  |

|        |                          |                | 217                                 | 216   | 215   | 214   | 213   | 212   | 211       | 210        | 1      |  |

| PSW51* | 80C51 compatible PSW     | 402h           | С                                   | AC    | F0    | RS1   | RS0   | V     | F1        | Р          | Note 6 |  |

| RSTSRC | Reset Source Reg         | 463h           | ROEN                                | -     | -     | -     | -     | R_WD  | R_CMD     | R_EXT      | Note 7 |  |

| RTH0   | Timer 0 Reload High      | 455h           |                                     |       |       |       |       |       |           |            | 00h    |  |

| RTH1   | Timer 1 Reload High      | 457h           |                                     | -     |       |       | -     | -     |           | -          | 00h    |  |

| RTL0   | Timer 0 Reload Low       | 454h           |                                     |       |       |       |       |       |           |            | 00h    |  |

| RTL1   | Timer 1 Reload Low       | 456h           |                                     |       |       |       |       |       |           |            | 00h    |  |

|        |                          |                |                                     |       |       |       | -     |       |           |            | 1      |  |

| SCR    | System Configuration Reg | 440h           | -                                   | -     | -     | -     | PT1   | PT0   | СМ        | PZ         | 00h    |  |

|        |                          |                | 21F                                 | 21E   | 21D   | 21C   | 21B   | 21A   | 219       | 218        |        |  |

| SSEL*  | Segment Selection Reg    | 403h           | ESWEN                               | R6SEG | R5SEG | R4SEG | R3SEG | R2SEG | R1SEG     | ROSEG      | 00h    |  |

|        |                          |                |                                     |       |       |       | I     |       |           |            | 1      |  |

### XA-SCC

### XA-SCC

| NAME   | DESCRIPTION                | SFR<br>Address | MSI  | В    | BIT FU | JNCTIONS | AND ADDR | ESSES |       | LSB  | RESET<br>VALUE |

|--------|----------------------------|----------------|------|------|--------|----------|----------|-------|-------|------|----------------|

| SWE    | Software Interrupt Enable  | 47Ah           | -    | SWE7 | SWE6   | SWE5     | SWE4     | SWE3  | SWE2  | SWE1 | 00h            |

|        |                            |                | 357  | 356  | 355    | 354      | 353      | 352   | 351   | 350  |                |

| SWR*   | Software Interrupt Request | 42Ah           | -    | SWR7 | SWR6   | SWR5     | SWR4     | SWR3  | SWR2  | SWR1 | 00h            |

|        |                            |                | 287  | 286  | 285    | 284      | 283      | 282   | 281   | 280  |                |

| TCON*  | Timer 0/1 Control          | 410h           | TF1  | TR1  | TF0    | TR0      | IE1      | IT1   | IE0   | IT0  | 00h            |

| TH0    | Timer 0 High               | 451h           |      |      |        |          |          |       |       |      | 00h            |

| TH1    | Timer 1 High               | 453h           |      |      |        |          |          |       |       |      | 00h            |

| TL0    | Timer 0 Low                | 450h           |      |      |        |          |          |       |       |      | 00h            |

| TL1    | Timer 1 Low                | 452h           |      | _    | -      |          | -        |       | -     |      | 00h            |

| TMOD   | Timer 0/1 Mode             | 45Ch           | GATE | C/T  | M1     | MO       | GATE     | C/T   | M1    | MO   | 00h            |

|        |                            |                | 28F  | 28E  | 28D    | 28C      | 28B      | 28A   | 289   | 288  |                |

| TSTAT* | Timer 0/1 Extended Status  | 411h           | -    | -    | -      | -        | -        | T1OE  | -     | TOOE | 00h            |

|        |                            |                | 2FF  | 2FE  | 2FD    | 2FC      | 2FB      | 2FA   | 2F9   | 2F8  |                |

| WDCON* | Watchdog Control           | 41Fh           | PRE2 | PRE1 | PRE0   | -        | -        | WDRUN | WDTOF | -    | Note 8         |

| WDL    | Watchdog Timer Reload      | 45Fh           |      |      |        |          |          |       |       |      | 00h            |

| WFEED1 | Watchdog Feed 1            | 45Dh           |      |      |        |          |          |       |       |      | xx             |

| WFEED2 | Watchdog Feed 2            | 45Eh           |      |      | -      |          | -        | -     | -     |      | хх             |

NOTES:

\* SFRs marked with an asterisk (\*) are bit addressable.

# SFRs marked with a pound sign (#) are additional SFR registers specific to the XA-SCC.

1. The XA-SCC implements an 8-bit SFR bus, as stated in Chapter 8 of the IC25 Data Handbook XA User Guide. All SFR accesses must be 8-bit operations. Attempts to write 16 bits to an SFR will actually write only the lower 8 bits. Sixteen bit SFR reads will return undefined data in the upper byte.

2. Unimplemented bits in SFRs are X (unknown) at all times. Ones should not be written to these bits since they may be used for other purposes in future XA derivatives. The reset value shown for these bits is 0.

3. The XA guards writes to certain bits (typically interrupt flags) that may be written by a peripheral function. This prevents loss of an interrupt or other status if a bit was written directly by a peripheral action between the read and write of an instruction that performs a read-modify-write operation. XA-SCC SFR bits that are guarded in this manner are: TF1, TF0, IE1, and IE0 (in TCON), and WDTOF (in WDCON).

4. Port configurations default to quasi-bidirectional when the XA begins execution after reset. Thus all PnCFGA registers will contain FFh and PnCFGB register will contain 00h. See warning in XA-SCC User Manual about P3.2\_Timer0\_ResetOut pin during first 258 clocks after power up. Basically, during this period, this pin may output a strongly driven low pulse. If the pulse does occur, it will terminate in a transition to high at a time no later than the 259th system clock after valid VCC power up.

5. SFR is loaded from the reset vector.

6. F1, F0, and P reset to 0. All other bits are loaded from the reset vector.

7. The RSTSRC register reflects the cause of the last XA reset. One bit will be set to 1, the others will be 0. RSTSRC[7] enables the ResetOut function; 1 = Enabled, 0 = Disabled. See XA-SCC User Manual for details; RSTSRC[7] differs in function from most other XA derivatives.

8. The WDCON reset value is E6 for a Watchdog reset, E4 for all other reset causes.

XA-SCC

### CMOS 16-bit communications microcontroller

### Table 2. Memory Mapped Registers

| MMR Name               | Read/Write or<br>Read Only | Size | Address<br>Offset | Description                                               | Reset<br>Value |

|------------------------|----------------------------|------|-------------------|-----------------------------------------------------------|----------------|

|                        |                            | SCC  | O Registers       |                                                           |                |

| SCC0 Write Register 0  | R/W                        | 8    | 800h              | Command register                                          | 00h            |

| SCC0 Write Register 1  | R/W                        | 8    | 802h              | Tx/Rx Interrupt & data transfer mode                      | xx             |

| SCC0 Write Register 2  | R/W                        | 8    | 804h              | Extended Features Control                                 | xx             |

| SCC0 Write Register 3  | R/W                        | 8    | 806h              | Receive Parameter and Control                             | 00h            |

| SCC0 Write Register 4  | R/W                        | 8    | 808h              | Tx/Rx misc. parameters & mode                             | 00h            |

| SCC0 Write Register 5  | R/W                        | 8    | 80Ah              | Tx. parameter and control                                 | 00h            |

| SCC0 Write Register 6  | R/W                        | 8    | 80Ch              | Sync character or SDLC address field or Match Character 0 | 00h            |

| SCC0 Write Register 7  | R/W                        | 8    | 80Eh              | Sync character or SDLC flag or Match Character 1          | xx             |

| SCC0 Write Register 8  | R/W                        | 8    | 810h              | Transmit Data Buffer                                      | xx             |

| SCC0 Write Register 9  | R/W                        | 8    | 812h              | Master Interrupt control                                  | xx             |

| SCC0 Write Register 10 | R/W                        | 8    | 814h              | Misc. Tx/Rx control register                              | 00h            |

| SCC0 Write Register 11 | R/W                        | 8    | 816h              | Clock Mode Control                                        | ХХ             |

| SCC0 Write Register 12 | R/W                        | 8    | 818h              | Lower Byte of Baud rate time constant                     | 00h            |

| SCC0 Write Register 13 | R/W                        | 8    | 81Ah              | Upper Byte of Baud rate time constant                     | 00h            |

| SCC0 Write Register 14 | R/W                        | 8    | 81Ch              | Misc. Control bits                                        | ХХ             |

| SCC0 Write Register 15 | R/W                        | 8    | 81Eh              | External/Status interrupt control                         | f8h            |

| SCC0 Write Register 16 | R/W                        | 8    | 828h              | Match Character 2 (WR16)                                  | 00h            |

| SCC0 Write Register 17 | R/W                        | 8    | 82Ah              | Match Character 3 (WR17)                                  | 00h            |

| SCC0 Read Register 0   | RO                         | 8    | 820h              | Tx/Rx buffer and external status                          | <u> </u>       |

| SCC0 Read Register 1   | RO                         | 8    | 822h              | Receive condition status/residue code                     | —              |

| Reserved-do not write  |                            |      | 824h              |                                                           | <u> </u>       |

| SCC0 Read Register 3   | RO                         | 8    | 826h              | Interrupt Pending Bits                                    | <u> </u>       |

| see WR16 and 17        |                            |      | 828–82Ah          | see WR16 and WR17 above                                   | <u> </u>       |

| SCC0 Read Register 6   | RO                         | 8    | 82Ch              | SDLC byte count low register                              | <u> </u>       |

| SCC0 Read Register 7   | RO                         | 8    | 82Eh              | SDLC byte count high & FIFO status                        | —              |

| SCC0 Read Register 8   | RO                         | 8    | 830h              | Receive Buffer                                            | —              |

| Reserved               |                            |      | 832h              |                                                           | —              |

| SCC0 Read Register 10  | RO                         | 8    | 834h              | Loop/clock status                                         | <u> </u>       |

| Reserved               |                            |      | 836–83Eh          |                                                           | <u> </u>       |

|                        | 1                          | scc  | 1 Registers       |                                                           |                |

| SCC1 Write Register 0  | R/W                        | 8    | 840h              | Command register                                          | 00h            |

| SCC1 Write Register 1  | R/W                        | 8    | 842h              | Tx/Rx Interrupt & data transfer mode                      | ХХ             |

| SCC1 Write Register 2  | R/W                        | 8    | 844h              | Extended Features Control                                 | xx             |

| SCC1 Write Register 3  | R/W                        | 8    | 846h              | Receive Parameter and Control                             | 00h            |

| SCC1 Write Register 4  | R/W                        | 8    | 848h              | Tx/Rx misc. parameters & mode                             | 00h            |

| SCC1 Write Register 5  | R/W                        | 8    | 84Ah              | Tx. parameter and control                                 | 00h            |

| SCC1 Write Register 6  | R/W                        | 8    | 84Ch              | Sync character or SDLC address field or Match Character 0 | 00h            |

| SCC1 Write Register 7  | R/W                        | 8    | 84Eh              | Sync character or SDLC flag or Match Character 1          | ХХ             |

| SCC1 Write Register 8  | R/W                        | 8    | 850h              | Transmit Data Buffer                                      | ХХ             |

| SCC1 Write Register 9  | R/W                        | 8    | 852h              | Master Interrupt control                                  | ХХ             |

| SCC1 Write Register 10 | R/W                        | 8    | 854h              | Misc. Tx/Rx control register                              | 00h            |

| SCC1 Write Register 11 | R/W                        | 8    | 856h              | Clock Mode Control                                        | ХХ             |

| SCC1 Write Register 12 | R/W                        | 8    | 858h              | Lower Byte of Baud rate time constant                     | 00h            |

| MMR Name               | Read/Write or<br>Read Only | Size | Address<br>Offset | Description                                               | Reset<br>Value |

|------------------------|----------------------------|------|-------------------|-----------------------------------------------------------|----------------|

| SCC1 Write Register 13 | R/W                        | 8    | 85Ah              | Upper Byte of Baud rate time constant                     | 00h            |

| SCC1 Write Register 14 | R/W                        | 8    | 85Ch              | Misc. Control bits                                        | ХХ             |

| SCC1 Write Register 15 | R/W                        | 8    | 85Eh              | External/Status interrupt control                         | f8h            |

| SCC1 Write Register 16 | R/W                        | 8    | 868h              | Match Character 2 (WR16)                                  | 00h            |

| SCC1 Write Register 17 | R/W                        | 8    | 86Ah              | Match Character 3 (WR17)                                  | 00h            |

| SCC1 Read Register 0   | RO                         | 8    | 860h              | Tx/Rx buffer and external status                          | - 1            |

| SCC1 Read Register 1   | RO                         | 8    | 862h              | Receive condition status/residue code                     | - 1            |

| Reserved               |                            |      | 864h              |                                                           |                |

| SCC1 Read Register 3   | RO                         | 8    | 866h              | Interrupt Pending Bits                                    | - 1            |

| see WR16 and 17        |                            |      | 868–86Ah          | see WR16 and WR17 above                                   | - 1            |

| SCC1 Read Register 6   | RO                         | 8    | 86Ch              | SDLC byte count low register                              | - 1            |

| SCC1 Read Register 7   | RO                         | 8    | 86Eh              | SDLC byte count high & FIFO status                        | <u> </u>       |

| SCC1 Read Register 8   | RO                         | 8    | 870h              | Receive Buffer                                            | _              |

| Reserved               |                            |      | 872h              |                                                           | -              |

| SCC1 Read Register 10  | RO                         | 8    | 874h              | Loop/clock status                                         | - 1            |

| Reserved               |                            |      | 876–87Eh          |                                                           | - 1            |

|                        |                            | scc  | 2 Registers       |                                                           |                |

| SCC2 Write Register 0  | R/W                        | 8    | 880h              | Command register                                          | 00h            |

| SCC2 Write Register 1  | R/W                        | 8    | 882h              | Tx/Rx Interrupt & data transfer mode                      | хх             |

| SCC2 Write Register 2  | R/W                        | 8    | 884h              | Extended Features Control                                 | хх             |

| SCC2 Write Register 3  | R/W                        | 8    | 886h              | Receive Parameter and Control                             | 00h            |

| SCC2 Write Register 4  | R/W                        | 8    | 888h              | Tx/Rx misc. parameters & mode                             | 00h            |

| SCC2 Write Register 5  | R/W                        | 8    | 88Ah              | Tx. parameter and control                                 | 00h            |

| SCC2 Write Register 6  | R/W                        | 8    | 88Ch              | Sync character or SDLC address field or Match Character 0 | 00h            |

| SCC2 Write Register 7  | R/W                        | 8    | 88Eh              | Sync character or SDLC flag or Match Character 1          | ХХ             |

| SCC2 Write Register 8  | R/W                        | 8    | 890h              | Transmit Data Buffer                                      | хх             |

| SCC2 Write Register 9  | R/W                        | 8    | 892h              | Master Interrupt control                                  | хх             |

| SCC2 Write Register 10 | R/W                        | 8    | 894h              | Misc. Tx/Rx control register                              | 00h            |

| SCC2 Write Register 11 | R/W                        | 8    | 896h              | Clock Mode Control                                        | хх             |

| SCC2 Write Register 12 | R/W                        | 8    | 898h              | Lower Byte of Baud rate time constant                     | 00h            |

| SCC2 Write Register 13 | R/W                        | 8    | 89Ah              | Upper Byte of Baud rate time constant                     | 00h            |

| SCC2 Write Register 14 | R/W                        | 8    | 89Ch              | Misc. Control bits                                        | хх             |

| SCC2 Write Register 15 | R/W                        | 8    | 89Eh              | External/Status interrupt control                         | f8h            |

| SCC2 Write Register 16 | R/W                        | 8    | 8A8h              | Match Character 2 (wr16)                                  | 00h            |

| SCC2 Write Register 17 | R/W                        | 8    | 8AAh              | Match Character 3 (wr17)                                  | 00h            |

| SCC2 Read Register 0   | RO                         | 8    | 8A0h              | Tx/Rx buffer and external status                          | - 1            |

| SCC2 Read Register 1   | RO                         | 8    | 8A2h              | Receive condition status/residue code                     | - 1            |

| Reserved               |                            |      | 8A4h              |                                                           | <u>  _ </u>    |

| SCC2 Read Register 3   | RO                         | 8    | 8A6h              | Interrupt Pending Bits                                    | <u> </u>       |

| see WR16 and 17        |                            |      | 8A8–8AAh          | see WR16 and WR17 above                                   | - 1            |

| SCC2 Read Register 6   | RO                         | 8    | 8ACh              | SDLC byte count low register                              | - 1            |

| SCC2 Read Register 7   | RO                         | 8    | 8AEh              | SDLC byte count high & FIFO status                        | - 1            |

| SCC2 Read Register 8   | RO                         | 8    | 8B0h              | Receive Buffer                                            | - 1            |

| Reserved               |                            |      | 8B2h              |                                                           | <u> </u>       |

| SCC2 Read Register 10  | RO                         | 8    | 8B4h              | Loop/clock status                                         | <u> </u>       |

| Reserved               |                            |      | 8B6-8BEh          | · · ·                                                     | <u> </u>       |

| MMR Name                               | Read/Write or<br>Read Only | Size  | Address<br>Offset | Description                                                                               | Reset<br>Value |

|----------------------------------------|----------------------------|-------|-------------------|-------------------------------------------------------------------------------------------|----------------|

|                                        | -                          | SCC   | 3 Registers       | -                                                                                         |                |

| SCC3 Write Register 0                  | R/W                        | 8     | 8C0h              | Command register                                                                          | 00h            |

| SCC3 Write Register 1                  | R/W                        | 8     | 8C2h              | Tx/Rx Interrupt & data transfer mode                                                      | хх             |

| SCC3 Write Register 2                  | R/W                        | 8     | 8C4h              | Extended Features Control                                                                 | ХХ             |

| SCC3 Write Register 3                  | R/W                        | 8     | 8C6h              | Receive Parameter and Control                                                             | 00h            |

| SCC3 Write Register 4                  | R/W                        | 8     | 8C8h              | Tx/Rx misc. parameters & mode                                                             | 00h            |

| SCC3 Write Register 5                  | R/W                        | 8     | 8CAh              | Tx. parameter and control                                                                 | 00h            |

| SCC3 Write Register 6                  | R/W                        | 8     | 8CCh              | Sync character or SDLC address field or Match Character 0                                 | 00h            |

| SCC3 Write Register 7                  | R/W                        | 8     | 8CEh              | Sync character or SDLC flag or Match Character 1                                          | ХХ             |

| SCC3 Write Register 8                  | R/W                        | 8     | 8D0h              | Transmit Data Buffer                                                                      | ХХ             |

| SCC3 Write Register 9                  | R/W                        | 8     | 8D2h              | Master Interrupt control                                                                  | ХХ             |

| SCC3 Write Register 10                 | R/W                        | 8     | 8D4h              | Misc. Tx/Rx control register                                                              | 00h            |

| SCC3 Write Register 11                 | R/W                        | 8     | 8D6h              | Clock Mode Control                                                                        | ХХ             |

| SCC3 Write Register 12                 | R/W                        | 8     | 8D8h              | Lower Byte of Baud rate time constant                                                     | 00h            |

| SCC3 Write Register 13                 | R/W                        | 8     | 8DAh              | Upper Byte of Baud rate time constant                                                     | 00h            |

| SCC3 Write Register 14                 | R/W                        | 8     | 8DCh              | Misc. Control bits                                                                        | хх             |

| SCC3 Write Register 15                 | R/W                        | 8     | 8DEh              | External/Status interrupt control                                                         | f8h            |

| SCC3 Write Register 16                 | R/W                        | 8     | 8E8h              | Match Character 2 (wr16)                                                                  | 00h            |

| SCC3 Write Register 17                 | R/W                        | 8     | 8EAh              | Match Character 3 (wr17)                                                                  | 00h            |

| SCC3 Read Register 0                   | RO                         | 8     | 8E0h              | Tx/Rx buffer and external status                                                          | - 1            |

| SCC3 Read Register 1                   | RO                         | 8     | 8E2h              | Receive condition status/residue code                                                     | —              |

| Reserved                               |                            |       | 8E4h              |                                                                                           | - 1            |

| SCC3 Read Register 3                   | RO                         | 8     | 8E6h              | Interrupt Pending Register                                                                | —              |

| SCC3 Read Register 6                   | RO                         | 8     | 8ECh              | SDLC byte count low register                                                              | —              |

| SCC3 Read Register 7                   | RO                         | 8     | 8EEh              | SDLC byte count high & FIFO status                                                        | —              |

| SCC3 Read Register 8                   | RO                         | 8     | 8F0h              | Receive Buffer                                                                            | —              |

| Reserved                               |                            |       | 8F2h              |                                                                                           | —              |

| SCC3 Read Register 10                  | RO                         | 8     | 8F4h              | Loop/clock status                                                                         | - 1            |

| Reserved                               |                            |       | 8F6–8FEh          |                                                                                           | —              |

|                                        | •                          | Rx DI | A Registers       | 5                                                                                         |                |

| DMA Control Register Ch.0 Rx           | R/W                        | 8     | 100h              | Control Register                                                                          | 00h            |

| FIFO Control & Status Reg Ch.0 Rx      | R/W                        | 8     | 101h              | Control & Status Register                                                                 | 00h            |